### **EXAMPLE 4-2**

.MODEL SMALL .STACK 200H ;set stack size

If the stack is not specified by using either method, a warning will appear when the program is linked. The warning may be ignored if the stack size is 128 bytes or fewer. The system automatically assigns (through DOS) at least 128 bytes of memory to the stack. This memory section is located in the program segment prefix (PSP), which is appended to the beginning of each program file. If you use more memory for the stack, you will erase information in the PSP that is critical to the operation of your program and the computer. This error often causes the computer program to crash. If the TINY memory model is used, the stack is automatically located at the very end of the segment, which allows for a larger stack area.

## 4-3 LOAD-EFFECTIVE ADDRESS

There are several load-effective address instructions in the microprocessor instruction set. The LEA instruction loads any 16-bit register with the address, as determined by the addressing mode selected for the instruction. The LDS and LES variations load any 16-bit register with the offset address retrieved from a memory location, and then load either DS or ES with a segment address retrieved from memory.

## LEA

The LEA instruction loads a 16- or 32-bit register with the offset address of the data specified by the operand. As the first example in Table 4–9 shows, the operand address NUMB is loaded into register AX, not the contents of address NUMB.

By comparing LEA with MOV, it is observed that LEA BX,[DI] loads the offset address specified by [DI] (contents of DI) into the BX register; MOV BX,[DI] loads the data stored at the memory location addressed by [DI] into register BX.

Earlier in the text, several examples are presented by using the OFFSET directive. The OFFSET directive performs the same function as an LEA instruction if the operand is a displacement. For example, the MOV BX,OFFSET LIST performs the same function as LEA BX,LIST. Both instructions load the offset address of memory location LIST into the BX register. See Example 4–3 for a short program that loads SI with the address of DATA1 and DI with the address of DATA2. It then exchanges the contents of these memory locations. Note that the LEA and MOV with OFFSET instructions are both the same length (three bytes).

ABLE 4-9 Load-effective address instructions.

| Assembly Language                                                        | Operation                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LEA AX,NUMB<br>LEA EAX,NUMB<br>LDS DI,LIST<br>LDS EDI,LIST<br>LES BX,CAT | Loads AX with the address of NUMB Loads EAX with the address of NUMB Loads DS and DI with the 32-bit contents of data segment memory location LIST Loads DS and EDI with the 48-bit contents of data segment memory location LIST Loads ES and BX with the 32-bit contents of data segment memory location CAT |

### **EXAMPLE 4-3**

|      |           | . MODEL | SMALL           | ;select SMALL model       |

|------|-----------|---------|-----------------|---------------------------|

| 0000 |           | .DATA   |                 | ;start of DATA segment    |

| 0000 | 2000 DA   | TA1 DW  | 2000H           | ;define DATA1             |

| 0002 | 3000 DA   | TA2 DW  | 3000Н           | ;define DATA2             |

| 0000 |           | .CODE   |                 | ;start of CODE segment    |

|      |           | .START  | UP              | ;start of program         |

| 0017 | BE 0000 R | LEA     | SI,DATA1        | ;address DATA1 with SI    |

| 001A | BF 0002 R | MOV     | DI,OFFSET DATA2 | ;address DATA2 with DI    |

| 001D | 8B 1C     | MOV     | BX,[SI]         | exchange DATA1 with DATA2 |

| 001B | 8B 0D     | MOV     | CX, [DI]        | , ,                       |

| 0021 | 89 OC     | MOV     | [SI],CX         |                           |

| 0021 | 89 1D     | MOV     | [DI],BX         |                           |

| 0023 | 05 15     | .EXIT   | [22],           | exit to DOS               |

|      |           | END     |                 | ;end of file              |

But why is the LEA instruction available if the OFFSET directive accomplishes the same task? First, OFFSET only functions with simple operands such as LIST. It may not be used for an operand such as [DI], LIST [SI], and so on. The OFFSET directive is more efficient than the LEA instruction for simple operands. It takes the microprocessor longer to execute the LEA BX,LIST instruction than the MOV BX,OFFSET LIST. The 80486 microprocessor, for example, requires two clocks to execute the LEA BX,LIST instruction and only one clock to execute MOV BX,OFFSET LIST. The reason that the MOV BX,OFFSET LIST instruction executes faster is because the assembler calculates the offset address of LIST, while the microprocessor calculates the LEA instruction. The MOV BX,OFFSET LIST instruction is actually assembled as a move immediate instruction and is more efficient.

Suppose that the microprocessor executes an LEA BX,[DI] instruction and DI contains a 1000H. Because DI contains the offset address, the microprocessor transfers a copy of DI into BX. A MOV BX,DI instruction performs this task in less time and is often preferred to the LEA BX,[DI] instruction.

Another example is LEA SI,[BX + DI]. This instruction adds BX to DI and stores the sum in the SI register. The sum generated by this instruction is a modulo-64K sum. If BX = 1000H and DI = 2000H, the offset address moved into SI is 3000H. If BX = 1000H and DI = FF00H, the offset address is 0F00H instead of 10F00H. Notice that the second result is a modulo-64K sum of 0F00H. (A **modulo-64K sum** drops any carry out of the 16-bit result.)

## LDS, LES,

The LDS and LES instructions load any 16-bit register with an offset address, and the DS, ES segment register with a segment address. These instructions use any of the memory-addressing modes to access a 32-bit section of memory that contains both the segment and offset address. The 32-bit section of memory contains a 16-bit offset and segment address.

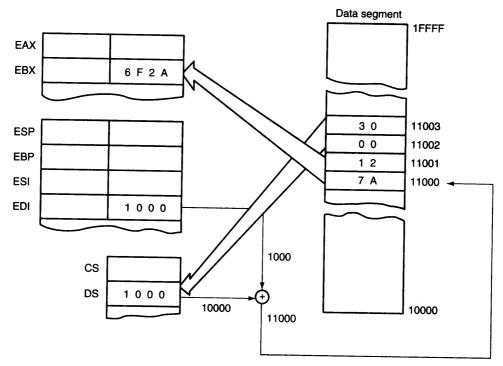

Figure 4–15 illustrates an example LDS BX,[DI] instruction. This instruction transfers the 32-bit number, addressed by DI in the data segment, into the BX and DS registers. The LDS and LES instructions obtain a new far address from memory. The offset address appears first, followed by the segment address. This format is used for storing all 32-bit memory addresses.

## 4–4 STRING DATA TRANSFERS

There are three string data transfer instructions: LODS, STOS, and MOVS. Each string instruction allows data transfers that are either a single byte, or word (or if repeated, a block of bytes, or words). Before the string instructions are presented, the operation of the D flag-bit (direction), DI, and SI must be understood as they apply to the string instructions.

**FIGURE 4–15** The LDS BX,[DI] instruction loads register BX from addresses 11000H and 11001H and register DS from locations 11002H and 11003H. This instruction is shown at the point just before DS changes to 3000H and BX changes to 127AH.

## The Direction Flag

The direction flag (D) (located in the flag register) selects the auto-increment (D = 0) or the auto-decrement (D = 1) operation for the DI and SI registers during string operations. The direction flag is used only with the string instructions. The CLD instruction clears the D flag (D = 0) and the STD instruction sets it (D = 1). Therefore, the CLD instruction selects the auto-increment mode (D = 0) and STD selects the auto-decrement mode (D = 1).

Whenever a string instruction transfers a byte, the contents of DI and/or SI increment or decrement by 1. If a word is transferred, the contents of DI and/or SI increment or decrement by 2. Only the actual registers used by the string instruction increment or decrement. For example, the STOSB instruction uses the DI register to address a memory location. When STOSB executes, only DI increments or decrements without affecting SI. The same is true of the LODSB instruction, which uses the SI register to address memory data. LODSB only increments/decrements SI without affecting DI.

### DI and SI

During the execution of a string instruction, memory accesses occur through either or both of the DI and SI registers. The DI offset address accesses data in the extra segment for all string instructions that use it. The SI offset address accesses data, by default, in the data segment. The segment assignment of SI may be changed with a segment override prefix, as described later in this chapter. The DI segment assignment is always in the extra segment when a string instruction executes. This assignment cannot be changed. The reason that one pointer addresses data in the

TABLE 4-10 Forms of the LODS instruction.

| Assembly Language | Operation                                          |

|-------------------|----------------------------------------------------|

| LODSB             | AL = DS:[SI]; SI = SI $\pm$ 1                      |

| LODSW             | AX = DS:[SI]; SI = SI $\pm$ 2                      |

| LODSD             | EAX = DS:[SI]; SI = SI $\pm$ 4                     |

| LODS LIST         | AL = DS:[SI]; SI = SI $\pm$ 1 (if LIST is a byte)  |

| LODS DATA1        | AX = DS:[SI], SI = SI $\pm$ 2 (if DATA1 is a word) |

Note: The segment can be overridden with a segment override prefix as in LODS ES:DATA4.

extra segment and the other in the data segment is so the MOVS instruction can move 64K bytes of data from one segment of memory to another.

## LODS

The LODS instruction loads AL, or AX, with data stored at the data segment offset address indexed by the SI register. After loading AL with a byte, AX with a word, or EAX with a doubleword, the contents of SI increment, if D = 0 or decrement, if D = 1. A 1 is added to or subtracted from SI for a byte-sized LODS, a 2 is added or subtracted for a word-sized LODS.

Table 4-10 lists the permissible forms of the LODS instruction. The LODSB (loads a byte) instruction causes a byte to be loaded into AL, the LODSW (loads a word) instruction causes a word to be loaded into AX. Although rare, as an alternative to LODSB, and LODSW, the LODS instruction may be followed by a byte-, wordsized operand to select a byte, or word transfer. Operands are often defined as bytes with DB and as words with DW. The DB pseudo-operation defines byte(s) and the DW pseudo-operation defines word(s).

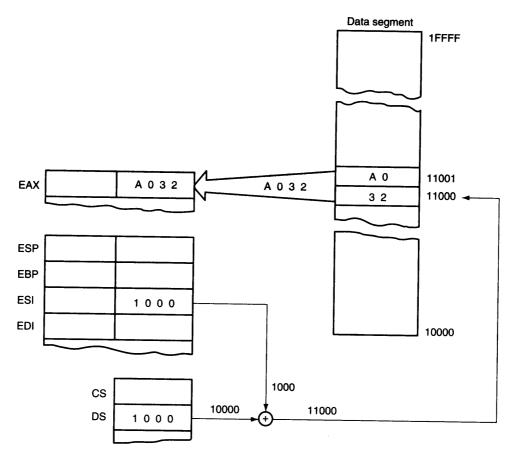

Figure 4–16 shows the effect of executing the LODSW instruction if the D flag = 0, SI = 1000H, and DS = 1000H. Here, a 16-bit number stored at memory locations 11000H and 11001H moves into AX. Because D = 0 and this is a word transfer, the contents of SI increment by 2 after AX loads with memory data.

### STOS

The STOS instruction stores AL, or AX at the extra segment memory location addressed by the DI register. Table 4-11 lists all forms of the STOS instruction. As with LODS, a STOS instruction may be appended with a B, or W for byte, or word transfers. The STOSB (stores a byte) instruction stores the byte in AL at the extra segment memory location addressed by DI. The STOSW (stores a word) instruction stores AX in the extra segment memory location addressed by DI. After the byte (AL), or word (AX) is stored, the contents of DI increments or decrements.

TABLE 4-11 Forms of the STOS instruction.

| Assembly Language | Operation                                          |

|-------------------|----------------------------------------------------|

| STOSB             | ES:[DI] = AL; DI = DI $\pm$ 1                      |

| STOSW             | ES:[DI] = AX; DI = DI $\pm$ 2                      |

| STOSD             | ES:[DI] = EAX; DI = DI $\pm$ 4                     |

| STOS LIST         | ES:[DI] = AL; DI = DI $\pm$ 1 (if list is a byte)  |

| STOS DATA3        | ES:[DI] = AX; DI = DI $\pm$ 2 (if DATA3 is a word) |

**FIGURE 4–16** The operation of the LODSW instruction if DS = 1000H, D = 0, 11000H = 32, and 11001H = A0. This instruction is shown after AX is loaded from memory, but before SI increments by 2.

**STOS with a REP.** The repeat prefix (REP) is added to any string data transfer instruction, except the LODS instruction. It doesn't make any sense to perform a repeated LODS operation. The REP prefix causes CX to decrement by 1 each time the string instruction executes. After CX decrements, the string instruction repeats. If CX reaches a value of 0, the instruction terminates and the program continues with the next sequential instruction. Thus, if CX is loaded with a 100, and a REP STOSB instruction executes, the microprocessor automatically repeats the STOSB instruction 100 times. Because the DI register is automatically incremented or decremented after each datum is stored, this instruction stores the contents of AL in a block of memory instead of a single byte of memory.

Suppose that the STOSW instruction is used to clear the video text display (see Example 4-4). This is accomplished by addressing video text memory that begins at memory location B800:0000. Each character position on the 25-line-by-80-character per line display comprises two bytes. The first byte contains the ASCII-coded character, and the second contains the color and attributes of the character. In this example, AL is the ASCII-coded space (20H) and AH is the color code for white text on a black background (07H). Notice how this program uses a count of 25 \* 80 and the REP STOSW instruction to clear the screen with ASCII spaces.

The operands in a program can be modified by using arithmetic or logic operators such as multiplication (\*). Other operators appear in Table 4–12.

TABLE 4-12 Common operand operators.

| Operator | Example          | Comment                                                    |

|----------|------------------|------------------------------------------------------------|

| +        | MOV AL,6+3       | Copies 9 into AL                                           |

| <u>.</u> | MOV AL,8-2       | Copies 6 into AL                                           |

| *        | MOV AL,4*3       | Copies 12 into AL                                          |

| 1        | MOV AX,12/5      | Copies 2 into AX (remainder is lost)                       |

| MOD      | MOV AX, 12 MOD 7 | Copies 5 into AX (quotient is lost)                        |

| AND      | MOV AX,12 AND 4  | Copies 4 into AX (1100 AND 0100 = 0100)                    |

| OR       | MOV AX,12 OR 1   | Copies 13 into AX (1100 OR 0001 = 1101)                    |

| NOT      | MOV AL,NOT 1     | Copies 254 into AL (0000 0001 NOT equals 1111 1110 or 254) |

### **EXAMPLE 4-4**

| 0000 |         | .MODEL TINY<br>.CODE<br>.STARTUP |           | <pre>;select TINY model ;start of CODE segment ;start of program</pre> |

|------|---------|----------------------------------|-----------|------------------------------------------------------------------------|

| 0100 | FC      | CLD                              |           | ;select increment mode                                                 |

| 0101 | B8 B800 | MOV                              | AX,0B800H | ;address segment B800                                                  |

| 0104 | 8E C0   | MOV                              | ES, AX    |                                                                        |

| 0106 | BF 0000 | MOV                              | DI,0      | ;address offset 0000                                                   |

| 0109 | B9 07D0 | MOV                              | CX,25*80  | ;load count                                                            |

| 010C | B8 0720 | MOV                              | AX,0720H  | ;load data                                                             |

| 010F | F3/AB   | REP<br>.EXIT<br>END              | STOSW     | <pre>;clear the screen ;exit to DOS ;end of file</pre>                 |

The REP prefix precedes the STOSW instruction in both assembly language and hexadecimal machine language. In machine language, the F3H is the REP prefix and ABH is the STOSW opcode.

If the value loaded to AX is changed to 0731H, the video display fills with white ones on a black background. If AX is changed to 0132H, the video display fills with blue twos on a black background. By changing the value loaded to AX, the display can be filled with any character and any color combination. More information on accessing the video display appears in a later chapter.

### MOVS

One of the more useful string data transfer instructions is MOVS because it transfers data from one memory location to another. This is the only memory-to-memory transfer allowed in the 8086-Pentium 4 microprocessors. The MOVS instruction transfers a byte, or word from the data segment location addressed by SI to the extra segment location addressed by DI. As with the other string instructions, the pointers then increment or decrement, as dictated by the direction flag. Table 4-13 lists all the permissible forms of the MOVS instruction. Note that only the source operand (SI), located in the data segment, may be overridden so that another segment may be used. The destination operand (DI) must always be located in the extra segment.

Suppose that the video display needs to be scrolled up one line. Because we now know the location of the video display, a repeated MOVSW instruction can be used to scroll the video display up a line. Example 4–5 lists a short program that addresses the video text display, beginning at location B800:0000 with the DS:SI register combination and location B800:00A0 with the ES:DI register combination. Next, the REP MOVSW instruction is executed 24 \* 80 times to scroll the display up a line. This is followed by a sequence that addresses the last line of the display so it can be cleared. The last line is cleared in this example by storing spaces on a black background. The last line could be cleared by changing only the ASCII code to a space, without modifying the attribute, by reading the

**TABLE 4–13** Forms of the MOVS instruction.

| Assembly Language | Operation                                                                          |  |  |

|-------------------|------------------------------------------------------------------------------------|--|--|

| MOVSB             | ES:[DI] = DS:[SI]; DI = DI $\pm$ 1; SI = SI $\pm$ 1 (byte transferred)             |  |  |

| MOVSW             | ES:[DI] = DS:[SI]; DI = DI $\pm$ 2; SI = SI $\pm$ 2 (word transferred)             |  |  |

| MOVS BYTE1,BYTE2  | ES:[DI] = DS:[SI]; DI = DI $\pm$ 1; SI = SI $\pm$ 1 (if BYTE1 and BYTE2 are bytes) |  |  |

| MOVS WORD1,WORD2  | ES:[DI] = DS:[SI]; DI = DI $\pm$ 2, SI = SI $\pm$ 2 (if WORD1 and WORD2 are words) |  |  |

code and attribute into a register. Once in a register, the code is modified, and both the code and attribute are stored in memory.

### **EXAMPLE 4-5**

| 0000<br>0100<br>0101<br>0104<br>0106 | FC<br>B8 B800<br>8E C0<br>8E D8        | .MODEL TINY .CODE .STARTUP CLD MOV MOV MOV | AX,0B800H<br>ES,AX<br>DS,AX              | ;select TINY model<br>;indicate start of CODE segment<br>;indicate start of program<br>;select increment<br>;load ES and DS with B800 |

|--------------------------------------|----------------------------------------|--------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 0108<br>010B<br>010E<br>0111         | BE 00A0<br>BF 0000<br>B9 0780<br>F3/A5 | MOV<br>MOV<br>MOV<br>REP                   | SI,160<br>DI,0<br>CX,24*80<br>MOVSW      | <pre>;address line 1 ;address line 0 ;load count ;scroll screen</pre>                                                                 |

| 0113<br>0116<br>0119<br>011C         | BF 0F00<br>B9 0050<br>B8 0720<br>F3/AB | MOV<br>MOV<br>MOV<br>REP<br>.EXIT<br>END   | DI,24*80*2<br>CX,80<br>AX,0720H<br>STOSW | <pre>;clear bottom line ;exit to DOS ;end of file</pre>                                                                               |

## 4-5 MISCELLANEOUS DATA TRANSFER INSTRUCTIONS

Don't be fooled by the term *miscellaneous;* these instructions are used in programs. The data transfer instructions detailed in this section are XCHG, LAHF, SAHF, XLAT, IN, and OUT. Because the miscellaneous instructions are not used as often as a MOV instruction, they have been grouped together and represented in this section.

### **XCHG**

The XCHG (exchange) instruction exchanges the contents of a register with the contents of any other register or memory location. The XCHG instruction cannot exchange segment registers or memory-to-memory data. Exchanges are byte-, word-, or doubleword-sized (80386 and above), and use any addressing mode discussed in Chapter 3, except immediate addressing. Table 4–14 shows some examples of the XCHG instruction.

The XCHG instruction, using the 16-bit AX register with another 16-bit register, is the most efficient exchange. This instruction occupies one byte of memory. Other XCHG instructions require two or more bytes of memory, depending on the addressing mode selected.

**TABLE 4–14** Forms of the XCHG instruction.

| Assembly Language             | Operation                                                                                                 |

|-------------------------------|-----------------------------------------------------------------------------------------------------------|

| XCHG AL, CL                   | Exchanges the contents of AL with CL                                                                      |

| XCHG CX, BP<br>XCHG AL, DATA2 | Exchanges the contents of CX with BP Exchanges the contents of AL with data segment memory location DATA2 |

When using a memory addressing mode and the assembler, it doesn't matter which operand addresses memory. The XCHG AL, [DI] instruction is identical to the XCHG [DI], AL instruction, as far as the assembler is concerned.

### LAHF and SAHF

The LAHF and SAHF instructions are seldom used because they were designed as bridge instructions. These instructions allowed 8085 (an early 8-bit microprocessor) software to be translated into 8086 software by a translation program. Because any software that required translation was probably completed many years ago, these instructions have little application today. The LAHF instruction transfers the rightmost eight bits of the flag register into the AH register. The SAHF instruction transfers the AH register into the rightmost eight bits of the flag register.

### **XLAT**

The XLAT (translate) instruction converts the contents of the AL register into a number stored in a memory table. This instruction performs the direct table lookup technique often used to convert one code to another. An XLAT instruction first adds the contents of AL to BX to form a memory address within the data segment. It then copies the contents of this address into AL. This is the only instruction that adds an 8-bit number to a 16-bit number.

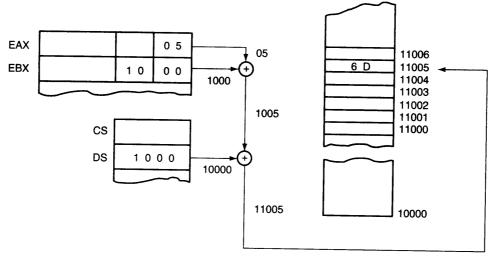

Suppose that a 7-segment LED display lookup table is stored in memory at address TABLE. The XLAT instruction then translates the BCD number in AL to a 7-segment code in AL. Example 4-6 provides a short program that converts from a BCD code to a 7-segment code. Figure 4-17 shows the operation of this example program if TABLE = 1000H, DS = 1000H, and the initial value of AL = 05H (a 5 BCD). After the translation, AL = 6DH.

### **EXAMPLE 4-6**

|      |             | ;Using an X<br>; | LAT to convert f | rom BCD to 7-segment code                     |

|------|-------------|------------------|------------------|-----------------------------------------------|

|      |             | .MODEL SMAL      | ıL               | ;select SMALL model<br>;start of DATA segment |

| 0000 |             | .DATA            |                  |                                               |

| 0000 | 3F 06 5B 4F | TABLE DB         | 3FH,6,5BH,4FH    |                                               |

| 0004 | 66 6D 7D 27 | DB               | 66H,6DH,7DH,2    | 7н                                            |

| 8000 | 7F 6F       | DB               | 7FH,6FH          |                                               |

| A000 | 00          | CODE7 DB         | ?                | ;reserve for result                           |

| 0000 |             | .CODE            |                  | ;start of CODE segment                        |

|      |             | .STARTUP         |                  | start of program;                             |

| 0017 | B0 04       | MOV              | AL,4             | ;load test data                               |

| 0019 | BB 0000 R   | MOV              | BX,OFFSET TAB    |                                               |

| 001C | D7          | XLAT             | 7                | ;convert to 7-segment                         |

| 001D | A2 000A R   | MOV              | CODE7,AL         | ;save 7-segment code                          |

|      |             | .EXIT            |                  | exit to DOS;                                  |

|      |             | END              |                  | end of file;                                  |

## IN and OUT

Table 4-15 lists the forms of the IN and OUT instructions, which perform I/O operations. Notice that the contents of AL, or AX are transferred only between the I/O device and the microprocessor. An IN instruction transfers data from an external I/O device to AL, or AX; an OUT transfers data from AL, or AX to an external I/O device.

**FIGURE 4–17** The operation of the XLAT instruction at the point just before 6DH is loaded into AL.

TABLE 4-15 IN and OUT instructions.

| Assembly Language | Operation                                 |  |  |

|-------------------|-------------------------------------------|--|--|

| IN AL,p8          | 8-bits are input to AL from I/O port p8   |  |  |

| IN AX,p8          | 16-bits are input to AX from I/O port p8  |  |  |

| IN AL,DX          | 8-bits are input to AL from I/O port DX   |  |  |

| IN AX,DX          | 16-bits are input to AX from I/O port DX  |  |  |

| OUT p8,AL         | 8-bits are output from AL to I/O port p8  |  |  |

| OUT p8,AX         | 16-bits are output from AX to I/O port p8 |  |  |

| OUT DX,AL         | 8-bits are output from AL to I/O port DX  |  |  |

| OUT DX,AX         | 16-bits are output from AX to I/O port DX |  |  |

Note: p8 = an 8-bit I/O port number and DX = the 16-bit port address held in DX.

Two forms of I/O device (port) addressing exist for IN and OUT: fixed-port and variable-port. Fixed-port addressing allows data transfer between AL or AX using an 8-bit I/O port address. It is called fixed-port addressing because the port number follows the instruction's opcode. Often, instructions are stored in a ROM. A fixed-port instruction stored in a ROM has its port number permanently fixed because of the nature of read-only memory. A fixed-port address stored in a RAM can be modified, but such a modification does not conform to good programming practices.

The port address appears on the address bus during an I/O operation. For the 8-bit fixed-port I/O instructions, the 8-bit port address is zero-extended into a 16-bit address. For example, if the IN AL,6AH instruction executes, data from I/O address 6AH are input to AL. The address appears as a 16-bit 006AH on pins A0-A15 of the address bus. Note that Intel reserves the last 16 I/O ports for use with some of its peripheral components.

Variable-port addressing allows data transfers between AL, AX, and a 16-bit port address. It is called *variable-port addressing* because the I/O port number is stored in register DX, which can be changed (varied) during the execution of a program. The 16-bit I/O port address appears on the address bus pin connections A0-A15. The IBM PC uses a 16-bit port address to access its I/O space. The I/O space for a PC is located at I/O port 0000H-03FFH. Note that some plug-in adapter cards may use I/O addresses above 03FFH.

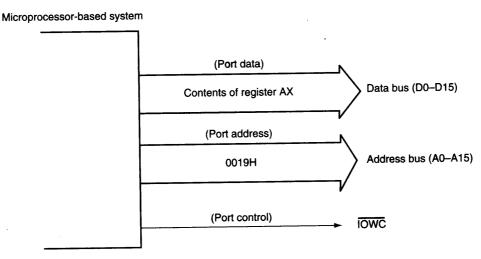

Figure 4–18 illustrates the execution of the OUT 19H,AX instruction, which transfers the contents of AX to I/O port 19H. Notice that the I/O port number appears as a 0019H on the 16-bit address bus and that the data from AX appears on the data bus of the microprocessor. The system control signal IOWC (I/O write control) is a logic zero to enable the I/O device.

A short program that clicks the speaker in the personal computer appears in Example 4–7. The speaker is controlled by accessing I/O port 61H. If the rightmost two bits of this port are set (11) and then cleared (00), a click is heard on the speaker. Note that this program uses a logical OR instruction to set these two bits and a logical AND instruction to clear them. These logic operation instructions are described in Chapter 5. The MOV CX,4000H instruction, followed by the LOOP L1 instruction, is used as a time delay. If the count is increased, the click will become longer; if shortened, the click will become shorter.

### **EXAMPLE 4-7**

| 0000 |         | .MODEL<br>.CODE<br>.STARTU |      |          | <pre>;select TINY model ;indicate start of code segment ;indicate start of program</pre> |

|------|---------|----------------------------|------|----------|------------------------------------------------------------------------------------------|

| 0100 | E4 61   |                            | IN   | AL,61H   | ;read port 61H                                                                           |

| 0102 | 0C 03   |                            | OR   | AL,3     | ;set rightmost two bits                                                                  |

| 0104 | E6 61   |                            | OUT  | 61H,AL   | ;speaker is on                                                                           |

|      |         |                            |      |          |                                                                                          |

| 0106 | B9 1000 |                            | VOM  | CX,1000H | ;delay count                                                                             |

| 0109 | 22      | L1:                        |      |          |                                                                                          |

| 0109 | E2 FE   |                            | LOOP | L1       | ;time delay                                                                              |

| 0103 | D2 1 D  |                            |      |          |                                                                                          |

| 010B | E4 61   |                            | IN   | AL,61H   | ;read port 61H                                                                           |

| 010D | 24 FC   |                            | AND  | AL, OFCH | clear rightmost two bits;                                                                |

|      |         |                            |      |          | ;speaker is off                                                                          |

| 010F | E6 61   |                            | OUT  | 61H,AL   | · -                                                                                      |

|      |         | .EXIT                      |      |          | exit to DOS;                                                                             |

|      |         | END                        |      |          | end of file;                                                                             |

**FIGURE 4–18** The signals found in the microprocessor-based system for an OUT 19H, AX instruction.

Assembly Language Segment Accessed Default Segment MOV AX, DS: [BP] Data Stack MOV AX,ES:[BP] Extra Stack MOV AX,SS:[DI] Stack Data MOV AX,CS:LIST Code Data MOV AX,ES:[SI] Extra Data LODS ES:DATA1 Data Extra

**TABLE 4–16** Instructions that include segment override prefixes.

## 4–6 SEGMENT OVERRIDE PREFIX

The segment override prefix, which may be added to almost any instruction in any memory addressing mode, allows the programmer to deviate from the default segment. The segment override prefix is an additional byte that appends the front of an instruction to select an alternate segment register. About the only instructions that cannot be prefixed are the jump and call instructions that must use the code segment register for address generation.

For example, the MOV AX, [DI] instruction accesses data within the data segment by default. If required by a program, this can be changed by prefixing the instruction. Suppose that the data are in the extra segment instead of in the data segment. This instruction addresses the extra segment if changed to MOV AX, ES:[DI].

Table 4–16 shows some altered instructions that address different memory segments that are different from normal. Each time an instruction is prefixed with a segment override prefix, the instruction becomes one byte longer. Although this is not a serious change to the length of the instruction, it does add to the instruction's execution time. It is usually customary to limit the use of the segment override prefix and remain in the default segments so that shorter and more efficient software can be written.

## 4-7 ASSEMBLER DETAIL

The assembler<sup>1</sup> for the microprocessor can be used in two ways: (1) with models that are unique to a particular assembler, and (2) with full segment definitions that allow complete control over the assembly process and are universal to all assemblers. This section of the text presents both methods, and explains how to organize a program's memory space by using the assembler. It also explains the purpose and use of some of the more important directives used with this assembler. Appendix A provides additional detail about the assembler.

### **Directives**

Before the format of an assembly language program is discussed, some details about the directives (**pseudo-operations**) that control the assembly process must be learned. Some common assembly language directives appear in Table 4–17. **Directives** indicate how an operand or section of a program is to be processed by the assembler. Some directives generate and store information in the memory, while others do not. The DB (**define byte**) directive stores bytes of data in the memory, while the BYTE PTR directive never stores data. The **BYTE PTR** directive indicates the size of the data referenced by a pointer or index register.

Note that the assembler by default accepts only 8086/8088 instructions, unless a program is preceded by the .386 or .386P directive or one of the other microprocessor selection switches. The .386 directive tells the assembler to use the 80386 instruction set in the real mode, while the .386P directive tells the assembler to use the 80386

<sup>&</sup>lt;sup>1</sup>The assembler used throughout this text is the Microsoft MACRO assembler MASM, version 6.X

TABLE 4-17 Common assembler directives.

| Directive | Function                                                                       |

|-----------|--------------------------------------------------------------------------------|

| .286      | Selects the 80286 instruction set; default is 8086                             |

| .386      | Selects the 80386 instruction set                                              |

| 486       | Selects the 80486 instruction set                                              |

| 586       | Selects the Pentium instruction set                                            |

| .287      | Selects the 80287 math coprocessor                                             |

| .387      | Selects the 80387 math coprocessor                                             |

| EXIT      | Exits to DOS                                                                   |

| MODEL     | Selects the programming model                                                  |

| STARTUP   | Indicates the start of the program when using program models                   |

| ASSUME    | Informs the assembler of the name of each segment for full segment definitions |

| BYTE      | Indicates byte-sized, as in BYTE PTR                                           |

| DB        | Defines byte(s) (8-bits)                                                       |

| DD        | Defines doubleword(s) (32-bits)                                                |

| DQ        | Defines quadword(s) (64-bits)                                                  |

| DT        | Defines ten byte(s) (80-bits)                                                  |

| DUP       | Generates duplicates                                                           |

| DW        | Defines word(s) (16-bits)                                                      |

| DWORD     | Indicates doubleword-sized, as in DWORD PTR                                    |

| END       | Ends a program file                                                            |

| ENDM      | Ends a macro sequence                                                          |

| ENDP      | Ends a procedure                                                               |

| ENDS      | Ends a segment or data structure                                               |

| EQU       | Equates data to a label                                                        |

| FAR       | Defines a far pointer                                                          |

| MACRO     | Designates the start of a macro sequence                                       |

| NEAR      | Defines a near pointer                                                         |

| OFFSET    | Specifies an offset address                                                    |

| ORG       | Sets the origin within a segment                                               |

| PROC      | Starts a procedure                                                             |

| PTR       | Designates a pointer                                                           |

| SEGMENT   | Starts a segment                                                               |

| STACK     | Starts a stack segment                                                         |

| STRUC     | Defines the start of a data structure                                          |

| WORD      | Indicates word-sized, as in WORD PTR                                           |

protected mode instruction set. Most software is written assuming that the microprocessor is an 80386 or newer, so the .386 switch is often used. Windows 95 was the first major operating system to use a 32-bit architecture that conforms to the 80386.

Storing Data in a Memory Segment. The DB (define byte), DW (define word), and DD (define doubleword) directives, first presented in Chapter 1, are most often used with the microprocessor to define and store memory data. If a numeric coprocessor executes software in the system, the DQ (define quadword) and DT (define ten bytes) directives are also common. These directives label a memory location with a symbolic name and indicate its size.

Example 4-8 shows a memory segment that contains various forms of data definition directives. It also shows the full segment definition with the first SEGMENT statement to indicate the start of the segment and its

4–7 ASSEMBLER DETAIL 113

symbolic name. Alternately, as in past examples in this and prior chapters, the SMALL model can be used with the .DATA statement. The last statement in this example contains the ENDS directive, which indicates the end of the segment. The name of the segment (LIST\_SEG) can be anything that the programmer desires to call it. This allows a program to contain as many segments as required.

### **EXAMPLE 4-8**

| 0000                                 |                                         | ;                    |                            | , DW, and DD direct:                      | ives                                                               |

|--------------------------------------|-----------------------------------------|----------------------|----------------------------|-------------------------------------------|--------------------------------------------------------------------|

| 0000                                 |                                         | LIST_S               | EG S                       | SEGMENT                                   |                                                                    |

| 0000<br>0003<br>0004<br>0005<br>0006 | 01 02 03<br>45<br>41<br>F0<br>000C 000D | DATA1                | DB<br>DB<br>DB<br>DB<br>DW | 1,2,3<br>45H<br>'A'<br>11110000B<br>12,13 | <pre>;define bytes ;hexadecimal ;ASCII ;binary ;define words</pre> |

| 000A<br>000C<br>000E<br>0012         | 0200<br>2345<br>00000300<br>4007DF3B    | DATA3                | DW<br>DW<br>DD<br>DD       | LIST1<br>2345H<br>300H                    | ;symbolic;hexadecimal;hexadecimal                                  |

| 0016<br>001A<br>001B                 | 544269E1<br>00<br>000A[                 | LISTA<br>LISTB<br>?? | DD<br>DB<br>DB             | 2.123<br>3.34E+12<br>?<br>10 DUP (?)      | <pre>;real ;real ;reserve 1 byte ;reserve 10 bytes</pre>           |

| 0025                                 | 00                                      | ]                    | ALIGN                      | 2                                         | ;set word boundary                                                 |

| 0026                                 | 0100[                                   | LISTC 0000           | DW                         | 100H DUP (0)                              | ;word array                                                        |

| 0226                                 | 0016[                                   | LIST_9               | DD                         | 22 DUP (?)                                | ;doubleword array                                                  |

| 027E                                 | 0064[                                   | SIXES                | ]<br>DB                    | 100 DUP (6)                               | ;byte array                                                        |

| 02E2                                 |                                         | ]<br>LIST_SE         | G ENDS                     |                                           |                                                                    |

Example 4–8 shows various forms of data storage for bytes at DATA1. More than one byte can be defined on a line in binary, hexadecimal, decimal, or ASCII code. The DATA2 label shows how to store various forms of word data. Doublewords are stored at DATA3; they include floating-point, single-precision real numbers.

Memory is **reserved** for use in the future by using a ? as an operand for a DB, DW, or DD directive. When a ? is used in place of a numeric or ASCII value, the assembler sets aside a location and does not initialize it to any specific value. (Actually, the assembler usually stores a zero into locations specified with a ?). The DUP (**duplicate**) directive creates an array, as shown in several ways in Example 4–8. A 10 DUP (?) reserves 10 locations of memory, but stores no specific value in any of the 10 locations. If a number appears within the () part of the DUP statement, the assembler initializes the reserved section of memory with the data indicated. For example, the DATA1 DB 10 DUP (2) instruction reserves 10 bytes of memory for array DATA1 and initializes each location with a 02H.

The ALIGN directive, used in this example, makes sure that the memory arrays are stored on word boundaries. It is important that word-sized data are placed at word boundaries and doubleword-sized data are placed at doubleword boundaries. If not, the microprocessor spends additional time accessing these data types. A word stored at an odd-numbered memory location takes twice as long to access as a word stored on an even-numbered memory location. Note that the ALIGN directive cannot be used with memory models because the size of the model determines

the data alignment. If all doubleword data are defined first, followed by word and then byte-sized data, the ALIGN statement is not necessary to align data correctly.

**ASSUME, EQU, and ORG.** The equate directive (EQU) equates a numeric, ASCII, or label to another label. Equates make a program clearer and simplify debugging. Example 4–9 shows several equate statements and a few instructions that show how they function in a program.

### **EXAMPLE 4-9**

```

;Using equate directive

;

= 000A TEN EQU 10

= 0009 NINE EQU 9

0000 BO 0A MOV AL,TEN

0002 04 09 ADD AL,NINE

```

The THIS directive always appears as THIS BYTE, THIS WORD, or THIS DWORD. In certain cases, data must be referred to as both a byte and a word. The assembler can only assign either a byte or a word address to a label. To assign a byte label to a word, use the software listed in Example 4–10.

### **EXAMPLE 4-10**

```

;Using the THIS and ORG directives

DATA_SEG

SEGMENT

0000

100H

0100

ORG

EOU

THIS BYTE

DATA1

= 0100

0100 0000

DATA2

DW

0102

DATA_SEG

ENDS

SEGMENT 'CODE'

CODE_SEG

0000

ASSUME CS:CODE_SEG,DS:DATA_SEG

MOV BL, DATA1

8A 1E 0100 R

0000

MOV AX, DATA2

A1 0100 R

0004

MOV BH, DATA1+1

0007

8A 3E 0101 R

CODE_SEG ENDS

000B

```

This example also illustrates how the ORG (origin) statement changes the starting offset address of the data in the data segment to location 100H. At times, the origin of data or the code must be assigned to an absolute offset address with the ORG statement. The ASSUME statement tells the assembler what names have been chosen for the code, data, extra, and stack segments. Without the ASSUME statement, the assembler assumes nothing and automatically uses a segment override prefix on all instructions that address memory data. The ASSUME statement is only used with full-segment definitions, as described later in this section of the text.

**PROC and ENDP.** The PROC and ENDP directives indicate the start and end of a procedure (**subroutine**). These directives *force structure* because the procedure is clearly defined. Note that if structure is to be violated for whatever reason, use the CALLF, CALLN, RETF, and RETN instructions. Both the PROC and ENDP directives require a label to indicate the name of the procedure. The PROC directive, which indicates the start of a procedure, must also be followed with a NEAR or FAR. A NEAR procedure is one that resides in the same code segment as the program. A FAR procedure may reside at any location in the memory system. Often the call NEAR procedure

4-7 ASSEMBLER DETAIL 115

is considered to be *local*, and the call FAR procedure is considered to be *global*. The term global denotes a procedure that can be used by any program, while local defines a procedure that is only used by the current program. Any labels that are defined within the procedure block are also defined as either local (NEAR) or global (FAR).

Example 4–12 shows a procedure that adds BX, CX, and DX and stores the sum in register AX. Although this procedure is short and may not be particularly useful, it does illustrate how to use the PROC and ENDP directives to delineate the procedure. Note that information about the operation of the procedure should appear as a grouping of comments that show the registers changed by the procedure and the result of the procedure.

### **EXAMPLE 4-11**

```

;A procedure that adds BX, CX, and DX with the sum

;stored in AX

0000

ADDEM

PROC

FAR

;start procedure

0000

03 D9

ADD

BX,CX

0002

03 DA

ADD

BX, DX

8B C3

0004

MOV

AX, BX

0006

CB

RET

0007

ADDEM ENDP

; end procedure

```

## **Memory Organization**

The assembler uses two basic formats for developing software: one method uses models and the other uses full-segment definitions. Memory models, as presented in this section and briefly in Chapters 2 and 3, are unique to the MASM assembler program. The TASM assembler also uses memory models, but they differ somewhat from the MASM models. The full-segment definitions are common to most assemblers, including the Intel assembler, and are often used for software development. The models are easier to use for simple tasks. The full-segment definitions offer better control over the assembly language task and are recommended for complex programs. The model was used in early chapters because it is easier to understand for the beginning programmer. Models are also used with assembly language procedures that are used by high-level languages such as C/C++. Although this text fully develops and uses the memory model definitions for its programming examples, realize that full-segment definitions offer some advantages over memory models, as discussed later in this section.

**Models.** There are many models available to the MASM assembler, ranging from tiny to huge. Appendix A contains a table that lists all the models available for use with the assembler. To designate a model, use the .MODEL statement followed by the size of the memory system. The **TINY model** requires that all software and data fit into one 64K-byte memory segment; it is useful for many small programs. The **SMALL model** requires that only one data segment be used with one code segment, for a total of 128K bytes of memory. Other models are available, up to the HUGE model.

Example 4–12 illustrates how the .MODEL statement defines the parameters of a short program that copies the contents of a 100-byte block of memory (LISTA) into a second 100-byte block of memory (LISTB). It also shows how to define the stack, data, and code segments. The .EXIT 0 directive returns to DOS with an error code of 0 (no error). If no parameter is added to .EXIT, it still returns to DOS, but the error code is not defined. Also note that special directives such as @DATA (see Appendix A) are used to identify various segments. If the .STARTUP directive is used (MASM version 6.X), the MOV AX,@DATA followed by MOV DS,AX statements can be eliminated. The .STARTUP directive also eliminates the need to store the starting address next to the END label. Models are important with both Microsoft C/C++ and Borland C/C++ development systems if assembly language is included with C/C++ programs. Both development systems use in-line assembly programming for adding assembly language instructions and require an understanding of programming models. Refer to the respective C/C++ language reference for each system to determine the model protocols.

## 116 CHAPTER 4 DATA MOVEMENT INSTRUCTIONS

### **EXAMPLE 4-12**

|                                      |                                                  |    | .MODEL<br>.STACK<br>.DATA |                                 |                                                       | ;define stack<br>;define data segment |

|--------------------------------------|--------------------------------------------------|----|---------------------------|---------------------------------|-------------------------------------------------------|---------------------------------------|

| 0000                                 | 0064[                                            | •• | LISTA                     | DB                              | 100 DUP (?)                                           |                                       |

| 0064                                 | 0064[                                            | ?? | listb                     | DB                              | 100 DUP (?)                                           |                                       |

|                                      |                                                  |    | .CODE                     |                                 |                                                       | ;define code segment                  |

| 0000<br>0003<br>0005                 | B8 R<br>8E C0<br>8E D8                           |    | HERE:                     | MOV<br>VOM                      | AX,@DATA<br>ES,AX<br>DS,AX                            | ;load ES, DS                          |

| 0007<br>0008<br>000B<br>000E<br>0011 | FC<br>BE 0000 R<br>BF 0064 R<br>B9 0064<br>F3/A4 |    |                           | CLD<br>MOV<br>MOV<br>MOV<br>REP | SI,OFFSET LISTA<br>DI,OFFSET LISTB<br>CX,100<br>MOVSB | ;move data                            |

| 0013                                 |                                                  |    | .EXIT                     |                                 |                                                       | ;exit to DOS                          |

Full-segment Definitions. Example 4–13 illustrates the same program, using full segment definitions. Full-segment definitions are also used with the Borland and Microsoft C/C++ environments for procedures developed in assembly language. The program in Example 4–13 appears longer than the one pictured in Example 4–12, but it is more structured than the model method of setting up a program. The first segment defined is the STACK\_SEG that is clearly delineated with the SEGMENT and ENDS directives. Within these directives, a DW 100 DUP (?) sets aside 100H words for the stack segment. Because the word STACK appears next to SEGMENT, the assembler and linker automatically load both the stack segment register (SS) and stack pointer (SP).

## **EXAMPLE 4-13**

| 0000 |       |      | STACK_S    | EG | SEGMENT STACK     |

|------|-------|------|------------|----|-------------------|

| 0000 | 0100[ | ???? | ]          | DW | 100H DUP (?)      |

| 0200 |       |      | STACK_S    | EG | ENDS              |

| 0000 |       |      | DATA_SE    | G  | SEGMENT 'DATA'    |

| 0000 | 0064[ | 22   | LISTA      | DB | 100 DUP (?)       |

| 0064 | 0064[ | ??   | l<br>LISTB | DB | 100 DUP (?)       |

| 00C8 |       |      | DATA_SE    | :G | ENDS              |

| 0000 |       |      | CODE_SE    | G  | SEGMENT 'CODE'    |

|      |       |      |            | AS | SUME CS:CODE SEG, |

ASSUME CS:CODE\_SEG,DS:DATA\_SEG ASSUME SS:STACK\_SEG 4–7 ASSEMBLER DETAIL 117

| 0000                                                                      | MAIN    | PROC                                | FAR                                          |                 |

|---------------------------------------------------------------------------|---------|-------------------------------------|----------------------------------------------|-----------------|

| 0000 B8 R<br>0003 8E C0<br>0005 8E D8                                     |         | MOV<br>MOV<br>MOV                   | AX, DATA_SEG<br>ES, AX<br>DS, AX             | ;load DS and ES |

| 0007 FC<br>0008 BE 0000 R<br>000B BF 0064 R<br>000E B9 0064<br>0011 F3/A4 |         | CLD<br>MOV<br>MOV<br>MOV<br>REP MOV | SI,OFFSET LISTA<br>DI,OFFSET LISTB<br>CX,100 | ;move data      |

| 0013 B4 4C<br>0015 CD 21                                                  |         | MOV<br>INT                          | AH,4CH<br>21H                                | ;exit to DOS    |

| 0017                                                                      | MAIN    | ENDP                                |                                              |                 |

| 0017                                                                      | CODE_SE | G END                               | s                                            |                 |

|                                                                           |         | END                                 | MAIN                                         |                 |

Next, the data are defined in the DATA\_SEG. Here, two arrays of data appear as LISTA and LISTB. Each array contains 100 bytes of space for the program. The names of the segments in this program can be changed to any name. Always include the group name 'DATA', so that the Microsoft program CodeView can be effectively used to symbolically debug this software. CodeView is a part of the MASM package used to debug software. To access CodeView, type CV, followed by the file name at the DOS command line; if operating from Programmer's WorkBench, select Debug under the Run menu. If the group name is not placed in a program, CodeView can still be used to debug a program, but the program will not be debugged in symbolic form. Other group names such as 'STACK', 'CODE', and so forth are listed in Appendix A. You must at least place the word 'CODE' next to the code segment SEGMENT statement if you want to view the program symbolically in CodeView.

The CODE\_SEG is organized as a far procedure because most software is procedure oriented. Before the program begins, the code segment contains the ASSUME statement. The ASSUME statement tells the assembler and linker that the name used for the code segment (CS) is CODE\_SEG; it also tells the assembler and linker that the data segment is DATA\_SEG and the stack segment is STACK\_SEG. Notice that the group name 'CODE' is used for the code segment for use by CodeView. Other group names appear in Appendix A with the models.

After the program loads both the extra segment register and data segment register with the location of the data segment, it transfers 100 bytes from LISTA to LISTB. Following this is a sequence of two instructions that return control back to DOS (the disk operating system). Note that the program loader does not automatically initialize DS and ES. These registers must be loaded with the desired segment addresses in the program.

The last statement in the program is END MAIN. The END statement indicates the end of the program and the location of the first instruction executed. Here, we want the machine to execute the main procedure so that a label follows the END directive.

## A Sample Program

Example 4–14 provides a sample program, using full-segment definitions, that reads a character from the keyboard and displays it on the CRT screen. Although this program is trivial, it illustrates a complete workable program that functions on any personal computer using DOS, from the earliest 8088-based system to the latest Pentium 4-based system. This program also illustrates the use of a few DOS function calls. (Appendix A lists the DOS function calls with their parameters.) The BIOS function calls allow the use of the keyboard, printer, disk drives, and everything else that is available in your computer system.

This example program uses only a code segment because there is no data. A stack segment should appear, but it has been left out because DOS automatically allocates a 128-byte stack for all programs. The only time that

the stack is used in this example is for the INT 21H instructions that call a procedure in DOS. Note that when this program is linked, the linker signals that no stack segment is present. This warning may be ignored in this example because the stack is fewer than 128 bytes.

Notice that the entire program is placed into a far procedure called MAIN. It is good programming practice to write all software in procedural form, which allows the program to be used as a procedure at some future time if necessary. It is also fairly important to document register use and any parameters required for the program in the program header, which is a section of comments that appear at the start of the program.

The program uses DOS functions 06H and 4CH. The function number is placed in AH before the INT 21H instruction executes. The 06H function reads the keyboard if DL = 0FFH, or displays the ASCII contents of DL if it is not 0FFH. Upon close examination, the first section of the program moves a 06H into AH and a 0FFH into DL, so that a key is read from the keyboard. The INT 21H tests the keyboard; if no key is typed, it returns equal. The JE instruction tests the equal condition and jumps to MAIN if no key is typed.

When a key is typed, the program continues to the next step, which compares the contents of AL with an @ symbol. Upon return from the INT 21H, the ASCII character of the typed key is found in AL. In this program, if an @ symbol is typed, the program ends. If the @ symbol is not typed, the program continues by displaying the character typed on the keyboard with the next INT 21H instruction.

The second INT 21H instruction moves the ASCII character into DL so it can be displayed on the CRT screen. After displaying the character, a JMP executes. This causes the program to continue at MAIN, where it repeats reading a key.

If the @ symbol is typed, the program continues at MAIN1, where it executes the DOS function code number 4CH. This causes the program to return to the DOS prompt (A>), so that the computer can be used for other tasks.

More information about the assembler and its application appears in Appendix A and in the next several chapters. Appendix A provides a complete overview of the assembler, linker, and DOS functions. It also provides a list of the BIOS (basic I/O system) functions. The information provided in the following chapters clarifies how to use the assembler for certain tasks at different levels of the text.

### **EXAMPLE 4-14**

|                                        | ;Note tha     | ple prog<br>at an @ | gram that reads a<br>key ends the prog | key and displays it.<br>gram. |

|----------------------------------------|---------------|---------------------|----------------------------------------|-------------------------------|

| 0000                                   | ;<br>CODE_SEG | SEGMI               | ENT 'CODE'                             |                               |

|                                        |               | ASSUME              | CS:CODE_SEG                            |                               |

| 0000                                   | MAIN          | PROC                | FAR                                    |                               |

| 0000 B4 06<br>0002 B2 FF<br>0004 CD 21 |               | MOV<br>MOV<br>INT   | AH,6<br>DL,0FFH<br>21H                 | ;read key                     |

| 0004 CD 21<br>0006 74 F8               |               | JE                  | MAIN                                   | ;if no key                    |

| 0008 3C 40<br>000A 74 08               |               | CMP<br>JE           | AL, '@'<br>MAIN1                       | ;test for @<br>;if @          |

| 000C B4 06<br>000E 8A D0<br>0010 CD 21 |               | MOV<br>MOV<br>INT   | ·                                      | ;display key                  |

| 0010 CB 21<br>0012 EB EC<br>0014       | MAIN1:        | JMP                 | MAIN                                   | ;repeat                       |

| 0014 B4 4C<br>0016 CD 21               | 11111111      | MOV<br>INT          | AH,4CH<br>21H                          | ;exit to DOS                  |

| 0018                                   | MAIN          | ENDP                |                                        |                               |

| 0018                                   | CODE_SEG      | END                 | os                                     |                               |

END MAIN

Example 4–15 shows the program listed in Example 4–16, except models are used instead of full-segment ssdescriptions. Please compare the two programs to determine the differences. Notice how much shorter the models can make a program.

### **EXAMPLE 4-15**

```

; An example program that reads a key and displays it.

; Note that an @ key ends the program.

.MODEL TINY

0000

.CODE

.STARTUP

0100

MAIN:

0100 B4 06

MOV AH, 6

;read key

0102 B2 FF

MOV DL, OFFH

0104 CD 21

INT 21H

0106 74 F8

JΕ

MAIN

; if no key

0108 3C 40

CMP AL. '@'

;text for @

010A 74 08

JE MAIN1

;if no @

010C B4 06

MOV AH, 6

; display key

010E 8A D0

MOV DL, AL

0110 CD 21

INT 21 H

0112 EB EC

JMP MAIN

;repeat

0114

MAIN1:

.EXIT

; exit to DOS

END

```

## 4-8 SUMMARY

- 1. Data movement instructions transfer data between registers, a register and memory, a register and the stack, memory and the stack, the accumulator and I/O, and the flags and the stack. Memory-to-memory transfers are allowed only with the MOVS instruction.

- 2. Data movement instructions include MOV, PUSH, POP, XCHG, XLAT, IN, OUT, LEA, LDS, LES, LAHF, SAHF; and the following string instructions: LODS, STOS, and MOVS.

- 3. The first byte of an instruction contains the opcode. The opcode specifies the operation performed by the microprocessor. The opcode may be preceded by one or more override prefixes in some forms of instructions.

- 4. The D bit, located in many instructions, selects the direction of data flow. If D = 0, the data flow from the REG field to the R/M field of the instruction. If D = 1, the data flow from the R/M field to the REG field.

- 5. The W bit, found in most instructions, selects the size of the data transfer. If W = 0, the data are byte-sized; if W = 1, the data are word-sized. In the 80386 and above, W = 1 specifies either a word or doubleword register.

- 6. MOD selects the addressing mode of operation for a machine language instruction's R/M field. If MOD = 00, there is no displacement; if MOD-01, an 8-bit sign-extended displacement appears; if MOD-10, a 16-bit displacement occurs; and if MOD-11, a register is used instead of a memory location. In the 80386 and above, the MOD bits also specify a 32-bit displacement.

- 7. A 3-bit binary register code specifies the REG and R/M fields when the MOD = 11. The 8-bit registers are AH, AL, BH, BL, CH, CL, DH, and DL. The 16-bit registers are AX, BX, CX, DX, SP, BP, DI, and SI.

- 8. When the R/M field depicts a memory mode, a 3-bit code selects one of the following modes: [BX+DI], [BX+SI], [BP+DI], [BP+SI], [BP], [DI], or [SI] for 16-bit instructions.

- 9. All memory-addressing modes, by default, address data in the data segment unless BP addresses memory. The BP register addresses data in the stack segment.

- 10. The segment registers are addressed only by the MOV, PUSH, or POP instructions. The MOV instruction may transfer a segment register to a 16-bit register, or vice versa. MOV CS,reg or POP CS instructions are not allowed because they change only part of the address. The 80386 through the Pentium 4 include two additional segment registers, FS and GS.

- 11. Data are transferred between a register or a memory location and the stack by the PUSH and POP instructions. Variations of these instructions allow immediate data to be pushed onto the stack, the flags to be transferred between the stack, and all 16-bit registers can be transferred between the stack and the registers. When data are transferred to the stack, two bytes (8086–80286) always move. The most-significant byte is placed at the location addressed by SP 1, and the least-significant byte is placed at the location addressed by SP 2. After placing the data on the stack, SP decrements by 2. In the 80386–Pentium 4, four bytes of data from a memory location or register may also be transferred to the stack.

- 12. Opcodes that transfer data between the stack and the flags are PUSHF and POPF. Opcodes that transfer all the 16-bit registers between the stack and the registers are PUSHA and POPA.

- 13. LEA, LDS, and LES instructions load a register or registers with an effective address. The LEA instruction loads any 16-bit register with an effective address; LDS and LES load any 16-bit register, and either DS or ES, with the effective address.

- 14. String data transfer instructions use either or both DI and SI to address memory. The DI offset address is located in the extra segment, and the SI offset address is located in the data segment.

- 15. The direction flag (D) chooses the auto-increment or auto-decrement mode of operation for DI and SI for string instructions. To clear D to 0, use the CLD instruction to select the auto-increment mode; to set D to 1, use the STD instruction to select the auto-decrement mode. Either or both DI and SI increment/decrement by 1 for a byte operation, by 2 for a word operation, and by 4 for a doubleword operation.

- 16. LODS loads AL or AX with data from the memory location addressed by SI; STOS stores AL or AX in the memory location addressed by DI; and MOVS transfers a byte or a word from the memory location addressed by SI into the location addressed by DI.

- 17. The REP prefix may be attached to any string instruction to repeat it. The REP prefix repeats the string instruction the number of times found in register CX.

- 18. Arithmetic and logic operators can be used in assembly language. An example is MOV AX, 34\*3, which loads AX with 102.

- 19. Translate (XLAT) converts the data in AL into a number stored at the memory location address by BX plus AL.

- 20. IN and OUT transfer data between AL or AX and an external I/O device. The address of the I/O device is either stored with the instruction (fixed port) or in register DX (variable port).

- 21. The segment override prefix selects a different segment register for a memory location than the default segment. For example, the MOV AX,[BX] instruction uses the data segment, but the MOV AX,ES:[BX] instruction uses the extra segment because of the ES: prefix.

- 22. Assembler directives DB, (define byte), DW (define word), DD (define doubleword), and DUP (duplicate) store data in the memory system.

- 23. The EQU (equate) directive allows data or labels to be equated to labels.

- 24. The SEGMENT directive identifies the start of a memory segment and ENDS identifies the end of a segment when full-segment definitions are in use.

- 25. The ASSUME directive tells the assembler what segment names you have assigned to CS, DS, ES, and SS when full-segment definitions are in effect.

- 26. The PROC and ENDP directives indicate the start and end of a procedure.

- 27. The assembler assumes that software is being developed for the 8086/8088 microprocessors unless the .286, .386, .486, or .586 directive is used to select one of these other microprocessors.

- 28. Memory models can be used to shorten the program slightly, but they can cause problems for larger programs. Also be aware that memory models are not compatible with all assembler programs.

## 4-9 QUESTIONS AND PROBLEMS

- 1. The first byte of an instruction is the \_\_\_\_\_\_, unless it contains one of the override prefixes.

- 2. Describe the purpose of the D- and W-bits found in some machine language instructions.

- 3. In a machine language instruction, what information is specified by the MOD field?

- 4. If the register field (REG) of an instruction contains a 010 and W = 0, what register is selected, assuming that the instruction is a 16-bit mode instruction?

- 5. What memory-addressing mode is specified by R/M = 001 with MOD = 00 for a 16-bit instruction?

- 6. Identify the default segment registers assigned to the following:

- (a) SP

- (b) BX

- (c) DI

- (d) BP

- (e) SI

- 7. Convert an 8B07H from machine language to assembly language.

- 8. Convert an 8B1E004CH from machine language to assembly language.

- 9. If a MOV SI, [BX+2] instruction appears in a program, what is its machine language equivalent?

- 10. What is wrong with a MOV CS, AX instruction?

- 11. Form a short sequence of instructions that load the data segment register with a 1000H.

- 12. The PUSH and POP instructions always transfer a(n) \_\_\_\_\_-bit number between the stack and a register or memory location in the 8086-microprocessors.

- 13. What segment register may not be popped from the stack?

- 14. Which registers move onto the stack with the PUSHA instruction?

- 15. Describe the operation of each of the following instructions:

- (a) PUSH AX

- (b) POP SI

- (c) PUSH [BX]

- (d) PUSHF

- (e) POP DS

- (f) PUSH 4

- 16. Explain what happens when the PUSH BX instruction executes. Make sure to show where BH and BL are stored. (Assume that SP = 0100H and SS = 0200H.)

- 17. Repeat question 16 for the PUSH AX instruction.

- 18. The 16-bit POP instruction (except for POPA) increments SP by \_\_\_\_\_.

- 19. What values appear in SP and SS if the stack is addressed at memory location 02200H?

- 20. Compare the operation of a MOV DI, NUMB instruction with an LEA DI, NUMB instruction.

- 21. What is the difference between an LEA SI, NUMB instruction and a MOV SI, OFFSET NUMB instruction?

- 22. Which is more efficient, a MOV with an OFFSET or an LEA instruction?

- 23. Describe how the LDS BX, NUMB instruction operates.

### 122 CHAPTER 4 DATA MOVEMENT INSTRUCTIONS

- 24. Develop a sequence of instructions that move the contents of data segment memory locations NUMB and NUMB+1 into BX, DX, and SI.

- 25. What is the purpose of the direction flag?

- 26. Which instructions set and clear the direction flag?

- 27. The string instructions use DI and SI to address memory data in which memory segments?

- 28. Explain the operation of the LODSB instruction.

- 29. Explain the operation of the STOSW instruction.

- 30. Explain the operation of the OUTSB instruction.

- 31. What does the REP prefix accomplish and what type of instruction is it used with?

- 32. Develop a sequence of instructions that copy 12 bytes of data from an area of memory addressed by SOURCE into an area of memory addressed by DEST.

- 33. Would the LAHF and SAHF instructions normally appear in software?

- 34. Explain how the XLAT instruction transforms the contents of the AL register.

- 35. Write a short program that uses the XLAT instruction to convert the BCD numbers 0-9 into ASCII-coded numbers 30H-39H. Store the ASCII-coded data in a TABLE located within the data segment.

- 36. Explain what the IN AL,12H instruction accomplishes.

- 37. Explain how the OUT DX, AX instruction operates.

- 38. What is a segment override prefix?

- 39. Select an instruction that moves a byte of data from the memory location addressed by the BX register, in the extra segment, into the AH register.

- 40. Develop a sequence of instructions that exchange the contents of AX with BX, CX with DX, and SI with DI.

- 41. What is an assembly language directive?

- 42. Describe the purpose of the following assembly language directives: DB, DW, and DD.

- 43. Select an assembly language directive that reserves 30 bytes of memory for array LIST1.

- 44. Describe the purpose of the EQU directive.

- 45. What is the purpose of the .386 directive?

- 46. What is the purpose of the .MODEL directive?

- 47. If the start of a segment is identified with .DATA, what type of memory organization is in effect?

- 48. If the SEGMENT directive identifies the start of a segment, what type of memory organization is in effect?

- 49. What does the INT 21H accomplish if AH contains a 4CH?

- 50. What directives indicate the start and end of a procedure?

- 51. Develop a near procedure that stores AL in four consecutive memory locations, within the data segment, as addressed by the DI register.

- 52. Develop a far procedure that copies contents of the word-sized memory location CS:DATA1 into AX, BX, CX, DX, and SI.

## **CHAPTER 5**

# Arithmetic and Logic Instructions

## INTRODUCTION

In this chapter, the arithmetic and logic instructions are examined. The arithmetic instructions include addition, subtraction, multiplication, division, comparison, negation, increment, and decrement. The logic instructions include AND, OR, Exclusive-OR, NOT, shifts, rotates, and the logical compare (TEST). The chapter concludes with a discussion of string comparison instructions, which are used for scanning tabular data and for comparing sections of memory data. Both tasks perform efficiently with the string scan (SCAS) and string compare (CMPS) instructions.

If you are familiar with an 8-bit microprocessor, you will recognize that the 8086 through the Pentium 4 instruction set is superior to most 8-bit microprocessors because most of the instructions have two operands instead of one. Even if this is your first microprocessor, you will quickly learn that this microprocessor possesses a powerful and easy-to-use set of arithmetic and logic instructions.

## **CHAPTER OBJECTIVES**

Upon completion of this chapter, you will be able to:

- 1. Use arithmetic and logic instructions to accomplish simple binary, BCD, and ASCII arithmetic.

- 2. Use AND, OR, and Exclusive-OR to accomplish binary bit manipulation.

- 3. Use the shift and rotate instructions.